Chip以封面文章发表电子科大杨世恒和澳门大学Pui-In Mak团队最新综述: 基于环形振荡器的锁相环时钟生成

FUTURE远见| 2023-06-16

Future|远见

Future|远见future选编

Chip第2卷第2期(2023年夏季刊)封面

Chip第2卷第2期(2023年夏季刊)封面随着SoC系统集成度越来越高、工艺制程越来越先进,需要的片上系统时钟的数量也随之增多,以此来满足系统不同模组丰富多样的需求如时钟同步、频率合成、调制解调等功能²⁻⁶。为优化面积,相比与传统的基于电感电容振荡器的锁相环,基于环形振荡器的锁相环结构因其突出的面积以及频率覆盖范围等优势,受到了越来越多的关注,目前也广泛地应用在各个领域发挥着关键作用。然而针对不同应用,需要提供不同性能侧重的时钟,通用的II型锁相环架构已不再适用,受限于供电电压较高、片上电容面积较大、功耗需求较大等问题。

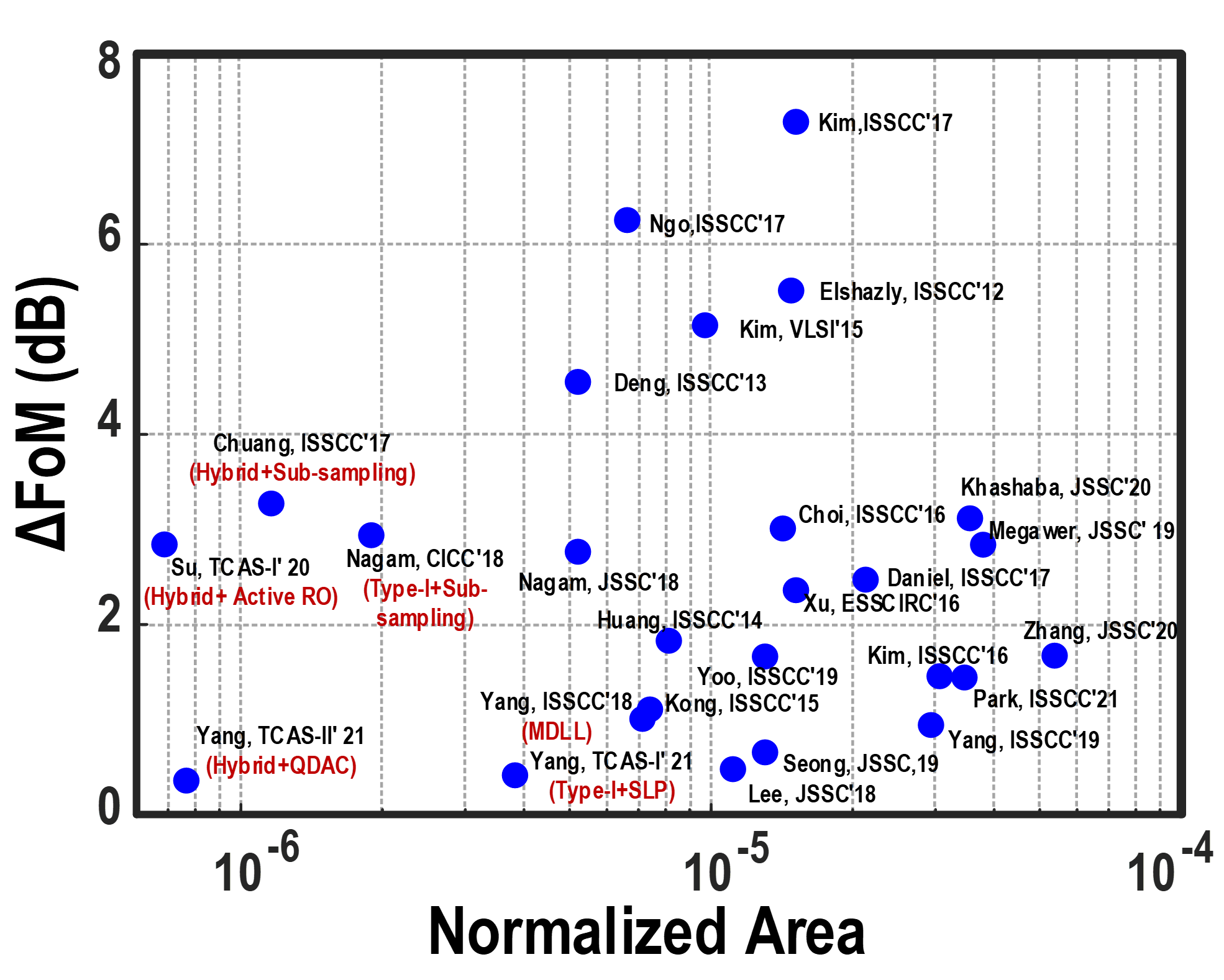

在本文中,研究者围绕不同的性能侧重(如功耗、时钟抖动以及面积),从环路架构层面,概述相关的电路技术和架构创新并进行分类比较,如图1和图2。其主要包括讨论低时钟抖动技术、面积减小技术、功耗与时钟抖动分析以及理论推导。例如注入锁定架构能获得较大带宽来抑制环形振荡器噪声;不同采样技术能在带宽、时钟抖动等方面呈现不一样的优势;模拟、数字电路的混合架构会在功耗、面积等方面实现更好的性能互补。根据对不同架构功耗、噪声等定量分析,能够更有效地判断出环路的理想性能。

图1 | 归一化面积与品质因子基准比较。

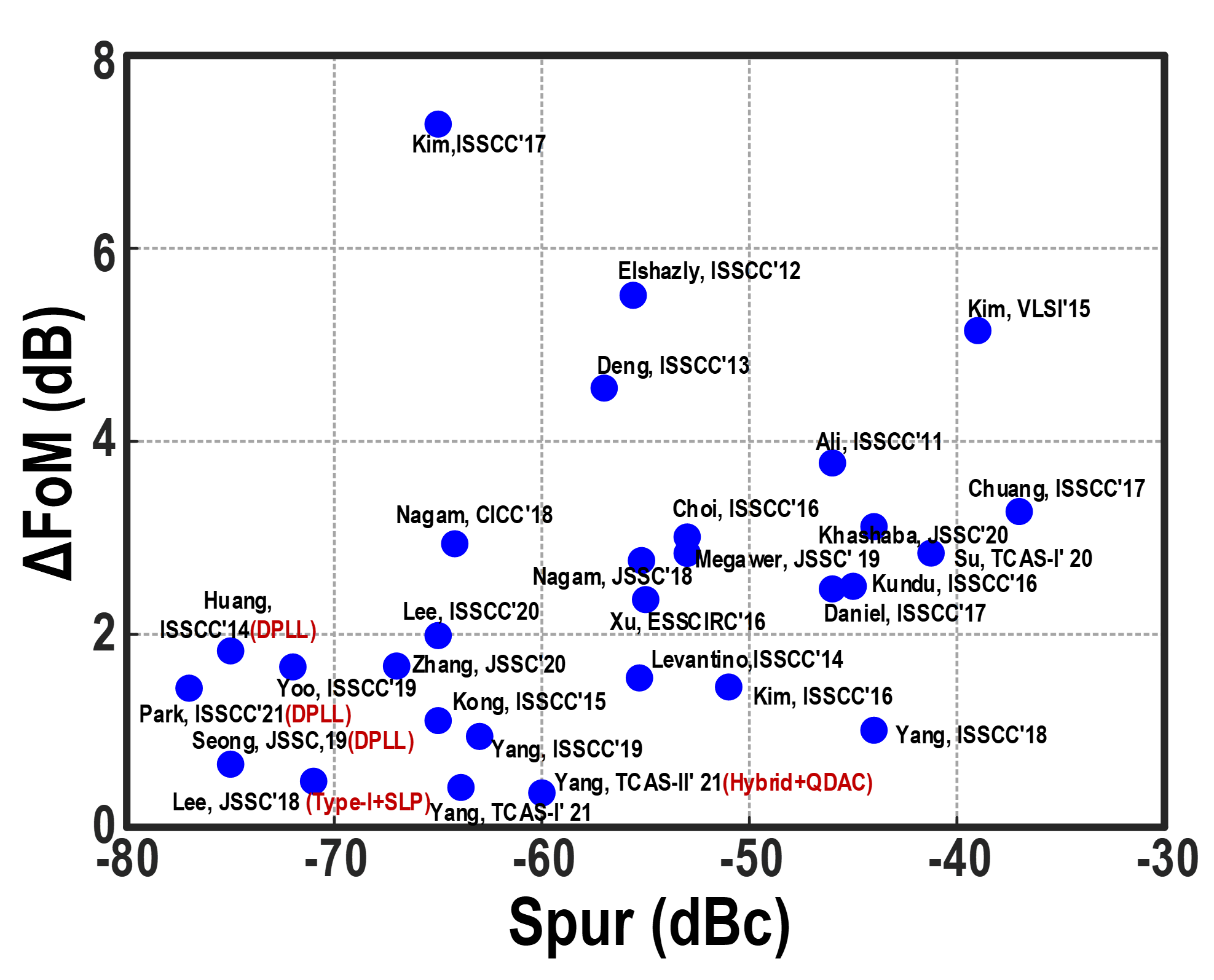

图1 | 归一化面积与品质因子基准比较。 图2 | 杂散与品质因子基准比较。

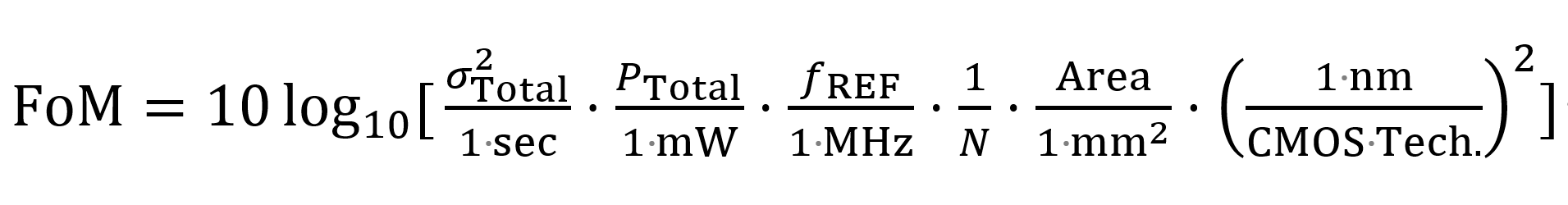

图2 | 杂散与品质因子基准比较。最后,为了更加公平地评价基于环形振荡器锁相环的设计指标,研究者完善了品质因子,其归一化品质因子公式如下所示:

对抖动、杂散、功耗、参考频率、分频比、工艺和面积等参数进行归一化比较。

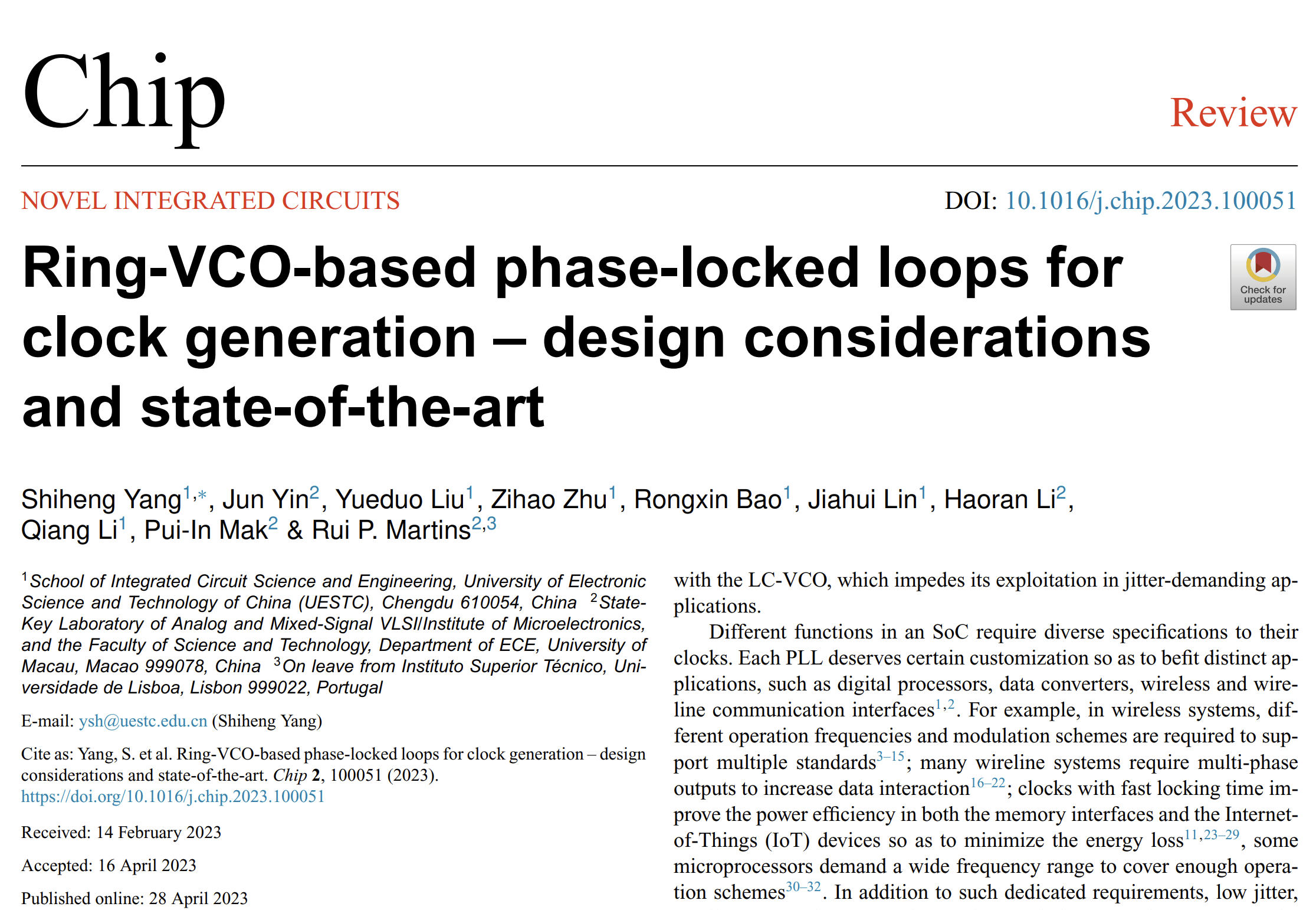

Ring-VCO-based phase-locked loops for clock generation–design considerations and state-of-the-art¹

As the technology scales down along with the system integration level is getting higher, the demand for clock generation is heavily increased ²⁻⁶. Compared with the LC-VCO-based phase-locked loops (PLL), ring voltage-controlled oscillator (VCO)-based PLL has the advantages of smaller area, less inductor coupling and wide tuning range, which attracts lots of interest.

This article overviews the design considerations and state-of-the-art of the VCO-based phase-locked loops (PLLs) for clock generation in different applications. Particularly, we aim to evaluate the required PLL performance among the fundamental metrics of power, jitter and area. An in-depth treatment of the mainstream PLL architectures and the associated design techniques enables us to compare them analytically, and benchmarks them with respect to their figure-of-merit (FoM) among power, area, jitter, spur and reference frequency.

We also summarize the key concerns on the selection of different circuit techniques for optimizing the clock performance under different scenarios. Such the injection-locked clock multiplier (ILCM) can intrinsically achieve a large bandwidth (BW) to effectively suppress the VCO PN. Various types of sampling techniques can obtain advantages among BW, jitter and power. The hybrid architecture of analog and digital circuits will accomplish better performance complementarity in terms of power consumption, area, etc.

论文链接:

https://www.sciencedirect.com/science/article/pii/S270947232300014X

参考文献

1. Yang, S. et al. Ring-VCO-based phase-locked loops for clock generation– design considerations and state-of-the-art. Chip 2, 100051 (2023).

2. Yang, S. et al. A 0.0056-mm² − 249-dB-FoM all-digital MDLL using a block-sharing offset-free frequency-tracking loop and dual multiplexed-ring VCOs. IEEE J. of Solid-State Circuits 54, 88–98 (2019).

3. Yang, S. et al. A 0.2-V energy-harvesting BLE transmitter with a micropower manager achieving 25% system efficiency at 0-dBm output and 5.2-nW sleep power in 28-nm CMOS. IEEE J. Solid-State Circuits 54, 1351–1362 (2019).

4. Yang, S. et al. A 600-μm² ring-VCO-based hybrid PLL using a 30-μW charge-sharing integrator in 28-nm CMOS. IEEE Trans. Circuits Syst. II: Express Br. 68, 3108–3112 (2021).

5. Gao, X. et al. A low noise sub-sampling PLL in which divider noise is eliminated and PD/CP noise is not multiplied by N². IEEE J. of Solid-State Circuits 44, 3253–3263 (2009).

6. Deng, W. et al. A fully synthesizable all-digital PLL with interpolative phase coupled oscillator, current-output DAC, and fine-resolution digital varactor using gated edge injection technique. IEEE J. of Solid-State Circuits 50, 68–80 (2014).

主要作者简介

杨世恒博士于2014和2019年分别获得澳门大学学士和博士学位,后分别担任澳门大学模拟与混合信号超大规模集成电路国家重点实验室研究助理、博士后研究员以及研究助理教授。现为电子科技大学“校百人计划”研究员,博士生导师。他的研究方向为模拟、射频集成电路设计,主要针对低功耗、高性能时钟等。

殷俊博士于2004和2007年分别获得北京大学微电子学士和硕士学位,并于2013年获得香港科技大学电子与计算机工程博士学位。现为澳门大学模拟与混合信号超大规模集成电路国家重点实验室副教授。殷俊博士现担任IEEE电路与系统会刊(TCAS-I)的副主编,国际固态电路会议(ISSCC)与欧洲固态电路会议(ESSCIRC)的技术委员会(TPC)成员。他的研究兴趣包括从射频到毫米波频率的时钟产生电路,以及应用于物联网的低功耗CMOS无线收发机。

Pui-In Mak(麦沛然),IEEE Fellow、IET Fellow、RSC Fellow、中国科学院海外专家、澳门大学微电子博士,现任澳门大学科技学院电机及计算机工程系教授、模拟与混合信号超大规模集成电路国家重点实验室主任和微电子研究院副院长(研究)。曾任IEEE,CASS和SSCS杰出演讲人和3个顶尖国际集成电路会议技术委员(ISSCC、ESSCIRC和A-SSCC)。2019年获国庆70周年纪念章和获选澳门彩车代表、2011年获国家科学技术进步二等奖、2005年获澳门政府授勋功绩奖状表彰他在科学上的贡献,2012年起6获澳门科技发明奖一、二等奖,2022年获腾讯科学探索奖。2011-2023年间连续13年发表ISSCC 论文共30篇和固态电路期刊JSSC论文35篇,麦教授现/曾担任多份 IEEE期刊高级/副/客座主编,包括《IEEE Press》《IEEE Journal of Solid-State Circuits》《IEEE Solid. State Circuits Letters》等。

Rui Paulo da Silva Martins(马许愿) ,IEEE会士,葡萄牙里斯本科学院院士,澳门大学副校长(全球事务),澳门大学微电子研究院院长,讲座教授。研究方向为电子学、模拟与混合信号超大规模集成电路等。其著作或合著共计896部(篇)出版物,包括:9部书籍及12个书籍篇章,745篇论文,其中331篇刊登于学术期刊中,414篇刊登于学术会议论文集中;另有其他学术作品80部(篇),h指数为46,引文数量为10000+。2003至2005年担任IEEE澳门分会创会主席;2005至2008年担任IEEE澳门电路与系统及通信联合分会创会主席(2009年IEEE电路与系统学会年度最佳分会);2008年IEEE亚太电路与系统学术会议大会主席;2009至2011年IEEE电路与系统学会第十区(亚洲、澳洲及太平洋)副主席,2012至2013年担任该学会的地区活动及会员(全球)副主席。2010至2013年,担任《IEEE Transactions on CAS II: Express Briefs》的副编辑,并获得该期刊2012至2013年度最佳副编辑的荣誉。2021年1月起,马许愿教授担任中国科学院半导体研究所《半导体物理学报》顾问委员会委员,并自2021年10月起成为亚太人工智能协会会士。他也是IEEE电路与系统学会会士评选委员会:2013、2014及2019年,成员;2018年,担任主席;2021及2022年,担任副主席;2014年IEEE第一组主任(电路与系统学会、电子设备学会和固态电路学会)提名委员会;2016至2017年电路与系统学会提名委员会。马许愿教授也是美国计算机协会及IEEE 2016年亚洲及南太平洋设计自动化研讨会大会主席,2016年获IEEE电子设计自动化委员会杰出服务奖;他担任2019年IEEE亚洲固态电路研讨会大会主席。他代表澳大于2005至2014年担任葡萄牙语大学联会副主席,2014至2017年担任主席,并于2021至2024年再次担任副主席。马许愿教授于2021年9月获AULP提名为名誉会员(此荣誉仅授予全球5人)。此外,他三次获得澳门政府荣誉:1999年获得澳葡政府授予的职业成就勋章,2001及2021年分別获得澳门特別行政区政府授予的功绩奖状及教育功绩勋章。2010年7月,马许愿教授以全票当选里斯本科学院通讯院士(2010-2022年)和有效院士(2022年起),是唯一一位在亚洲工作和生活的葡萄牙院士。

关于Chip

Chip是全球唯一聚焦芯片类研究的综合性国际期刊,已入选由中国科协、教育部、科技部、中科院等单位联合实施的「中国科技期刊卓越行动计划高起点新刊项目」,为科技部鼓励发表「三类高质量论文」期刊之一。

Chip期刊由上海交通大学与Elsevier集团合作出版,并与多家国内外知名学术组织展开合作,为学术会议提供高质量交流平台。

Chip秉承创刊理念: All About Chip,聚焦芯片,兼容并包,旨在发表与芯片相关的各科研领域尖端突破性成果,助力未来芯片科技发展。迄今为止,Chip已在其编委会汇集了来自14个国家的70名世界知名专家学者,其中包括多名中外院士及IEEE、ACM、Optica等知名国际学会终身会士(Fellow)。

Chip第二卷第二期(2023年夏刊)即将于2023年6月在爱思维尔Chip官网以金色开放获取形式(Gold Open Access)发布,欢迎访问阅读本期最新文章。

爱思唯尔Chip官网:

https://www.journals.elsevier.com/chip