Chip10 Science | 基于事件驱动视觉传感器的脉冲神经网络

FUTURE远见| 2024-04-08

Future|远见

Future|远见future选编

工作简介

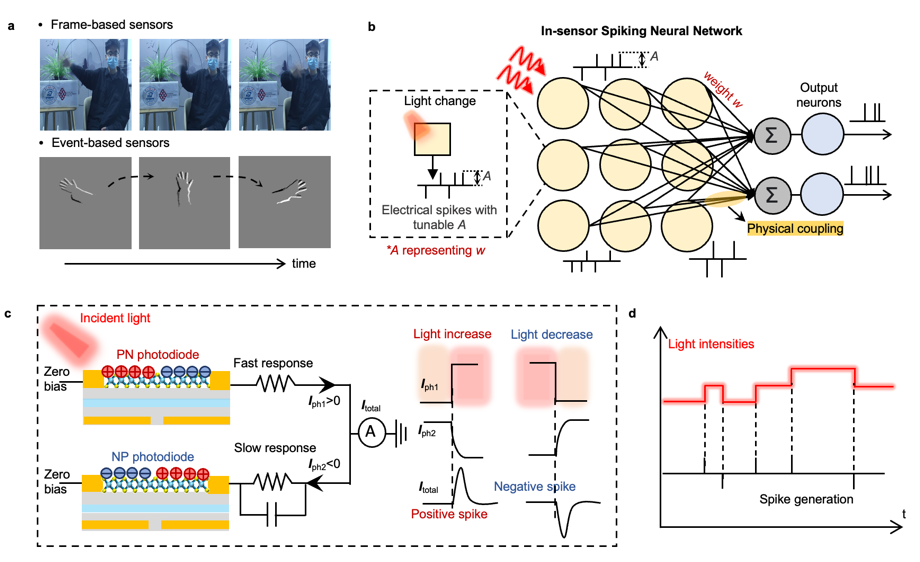

传统的图像传感器具有固定的帧率,无论像素点的光强有没有发生变化,都会在每一帧记录下所有像素的绝对光强,因此包含了大量的冗余视觉数据和有限的信息。基于事件的视觉传感器只有在像素点发生光强变化的时刻才会发放一个脉冲信号,当处于一个动态变化的场景时会异步地发放一系列稀疏的脉冲序列,产生很少但是包含有价值的数据。目前市面上已经存在的神经形态视觉传感器(DVS),首先需要用包含了光电探测器、电容器、放大器和比较器等复杂的像素电路检测光强的变化。然后这些模拟信号需要经过ADC转化为数字信号,最后被FPGA 标上时间戳,产生一系列包含像素地址, 光强变化极性(光强增加或者减小),时间信息的数字事件。这些由ADC 和FPGA 完成的模拟信号处理步骤限制 DVS 的时间分辨率在几十微秒量级。除此之外,经过处理后的数字信号仍然需要被频繁地传输到基于脉冲的神经形态处理器或者由电子突触构建的脉冲神经网络中。数字信号在传感器和处理单元之间的传输进一步把时间分辨率限制在毫秒量级。

通过直接在传感端进行视觉信息的处理可以在理论上显著提高时间效率和能效。有工作表明通过在传感端的预处理(近传感器计算),比如增强对比度,减小噪声,视觉自适应调节等,可以显著提高图像识别效率。为了直接在传感器内做更高级别任务如图像识别,实现传感器内计算, 研究人员们直接用可调节的光响应度来模拟突触权重,用光探测器构建了人工神经网络执行静态图像识别任务。但这些工作又受限于人工神经网络,每个像素对绝对光强值产生对应的光电流值,针对动态场景如动作识别等缺乏事件触发特性,会产生大量冗余的数据。

图1 事件驱动的感存算一体脉冲神经网络。a,传统基于帧和事件驱动的视觉传感器的对比。基于帧的传感器以固定的帧率记录所有像素,包括动态运动和静态背景,而事件驱动传感器异步地捕获单个像素的光强变化。b, 通过结合事件驱动特性和传感器内计算的优势设计的感存算一体脉冲神经网络。当光强变化时,传感器像素单元产生可编程的电脉冲。c, 两个互补分支在光强保持恒定时总输出光电流为零,当光强变化时两个分支的光响应时间差导致总输出为光电流脉冲。d, 输入光强与输出脉冲之间的关系。

图2 基于WSe₂光电二极管的像素单元中可调的事件驱动特性。a, 像素电路中一个分支的示意图。b, 在一系列光脉冲下的光响应。通过引入不同大小的电容器可调节延时。c, PN和d, NP结光电二极管的光响应时间。e, 带有两个互补电路分支的像素单元示意图。一个分支是WSe₂ PN光电二极管,另一个是NP光电二极管。f, 通过对栅极施加电压脉冲对WSe₂沟道进行局部编程从而将光电二极管调制为不同的光响应性,实现相同光脉冲下的可调节电脉冲幅度(光强为25 mW cm⁻²,光脉冲宽度为300 μs)。g, 随着光强逐步增加(减小),产生两个正(负)脉冲。h, 实现负突触权重的像素电路示意图,通过交换两个电路分支中WSe₂光电二极管的配置来实现。i, 通过将光电二极管编程为更大的光响应性,实现更负的权重。j, 光强增加(减小)时,产生负(正)脉冲。所有测量(b-d、f、g、i、j)均在栅极和源极电压偏置为零的情况下进行,显示出自驱动特性。

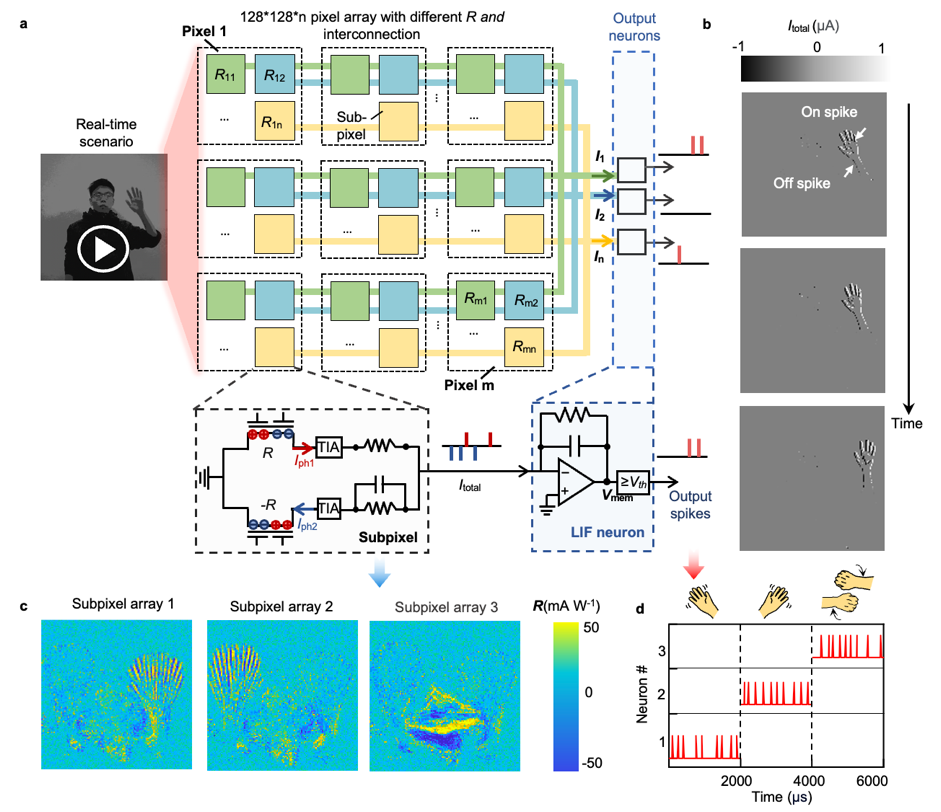

图3 用于运动识别的感存算一体脉冲神经网络。a,事件驱动的脉冲神经网络像素阵列示意图以及相应的单个像素和输出神经元的电路图。b,执行动作时像素单元输出的总光电流。仅在光强变化的区域产生正或负的电流脉冲。c,训练后每个子像素阵列的光响应分布。每个子像素阵列均在不同的特定区域具有较强的光响应分布,表明对动作具有不同的灵敏度。d,当依次执行左手挥动、右手挥动和环绕手臂时,输出神经元产生的输出脉冲。

因此本工作结合神经形态视觉传感器和感存算一体化的优点,开发适用于动作识别的感存算一体 SNN 架构,设计出一种基于事件驱动的像素单元,可以在光强变化时产生可编程的脉冲信号。通过调节光电探测器的光响应度可以有效调节像素单元产生的脉冲信号的幅度,从而模拟不同的突触权重。该工作中,光感应材料选用WSe₂。WSe₂具有较强的静电掺杂调控能力,由于金属/WSe₂界面处较弱的费米能级钉扎,WSe₂容易被电场调节为n型或者p型从而具有双极性。其次,WSe₂作为具有原子级别厚度的半导体具有较强的光-物质交互作用。通过对两个局部背栅分别施加正负电压,调节储存在浮栅层HfO₂的电子和空穴数量。诱导沟道WSe₂左右两个区域的载流子类型和浓度,形成具有不同整流效应的PN结或NP结,从而具有可调节的正负光响应度。光的照射激发电子空穴对的产生,并被WSe₂构成的PN结和NP结的内建电场所分开。因此,即使在零偏压的情况下基于WSe₂的PN或者NP结也会产生自驱动短路光电流,具有微秒级别的响应时间。

相比较传统计算架构需要传感单元和计算单元之间的来回传输,造成毫秒级别的延迟,我们的感存算一体方案,直接在传感器内执行计算,其动作识别的延迟仅局限于WSe₂的响应时间,因此本工作设计的传感器内计算架构可以实现低于20 μs 的时间分辨率。进一步地,通过对车道保持和动作识别的仿真我们验证了其发展为实时处理的低功耗的智能视觉芯片的潜力。

论文链接:

https://www.nature.com/articles/s41928-023-01055-2

通讯作者简介

柴扬,香港理工大学应用物理系教授,香港理工大学理学院副院长,香港物理学会副主席,香港青年科学院院士,IEEE Distinguished Lecturer,IEEE EDS Nanotechnology Committee主席。研究兴趣主要为新型微电子器件。

何毓辉,2009年获北京大学微电子专业博士学位,先后在中国科学院微电子研究所、日本大阪大学产业科学研究所从事博士后研究,2015年入职华中科技大学微电子系,长期从事微纳电子学与生物学的交叉研究,如固态纳米孔基因测序、神经形态器件与计算等。

第一作者简介

周越,2018年6月获华中科技大学光学与电子信息学院学士学位。2023年6月获华中科技大学集成电路学院博士学位。2021年6月到2023年10月之间赴香港理工大学交流学习,目前为美国加州大学圣地亚阿哥分校博士后。博士期间以第一作者,共同第一作者的身份在Nature Electronics, Advanced Materials, Advanced Functional Materials, IEEE Transactions on Neural Networks and Learning Systems等顶级期刊,以及微电子领域顶级会议IEEE International Electron Devices Meeting (IEDM)上均发表相关工作,目前以共同作者身份成功发表论文二十余篇。

关于Chip

Chip(ISSN:2772-2724,CN:31-2189/O4)是全球唯一聚焦芯片类研究的综合性国际期刊,已入选由中国科协、教育部、科技部、中科院等单位联合实施的「中国科技期刊卓越行动计划高起点新刊项目」,为科技部鼓励发表「三类高质量论文」期刊之一。

Chip期刊由上海交通大学出版,联合Elsevier集团全球发行,并与多家国内外知名学术组织展开合作,为学术会议提供高质量交流平台。

Chip秉承创刊理念: All About Chip,聚焦芯片,兼容并包,旨在发表与芯片相关的各科研领域尖端突破性成果,助力未来芯片科技发展。迄今为止,Chip已在其编委会汇集了来自14个国家的69名世界知名专家学者,其中包括多名中外院士及IEEE、ACM、Optica等知名国际学会终身会士(Fellow)。

Chip第三卷第一期已于2024年3月在爱思维尔Chip官网以金色开放获取形式(Gold Open Access)发布,欢迎访问阅读本期最新文章。

爱思唯尔Chip官网:

https://www.sciencedirect.com/journal/chip